# TSW3100 High Speed Digital Pattern Generator

#### Contents

| 1 | Hardv | vare Configuration                          | 2  |

|---|-------|---------------------------------------------|----|

|   | 1.1   | Power Input Source                          | 3  |

|   | 1.2   | Output Power Regulators                     | 3  |

|   | 1.3   | Switches and LEDs                           | 3  |

|   | 1.4   | Input and Output Connectors                 | 4  |

| 2 | Softw | are Installation                            | 8  |

|   | 2.1   | USB to Ethernet Adapter Installation        | 8  |

|   | 2.2   | Configure the USB to Ethernet network       | 9  |

|   | 2.3   | Installing the MATLAB Runtime Engine        | 11 |

|   | 2.4   | Installing the TSW3100 Application Software | 14 |

|   | 2.5   | Starting the TSW3100 Application Software   | 16 |

| 3 | Apply | Power to TSW3100 and Connect to a Host      | 17 |

| 4 |       | Interface                                   |    |

|   | 4.1   | TSW3100 IP Address                          | 17 |

|   | 4.2   | TSW3100 Control Files                       | 18 |

|   | 4.3   | TSW3100 Data Pattern Format                 | 18 |

|   | 4.4   | TSW3100 Operation Sequence                  | 18 |

|   | 4.5   | TSW3100 Connection to LVDS HSDAC EVM        | 19 |

|   | 4.6   | TSW3100 Connection to CMOS HSDAC EVMs       | 20 |

|   | 4.7   | TSW3100 Master/Slave Operation              | 21 |

| 5 | Exam  | ple MATLAB Functions for TSW3100 Control    | 21 |

|   | 5.1   | LVDS Pattern File Generation                | 21 |

|   | 5.2   | CMOS Pattern File Generation                | 22 |

|   | 5.3   | Pattern File Loading to TSW3100             | 22 |

|   | 5.4   | Running the TSW3100                         | 26 |

| 6 | Gene  | rating LVDS and CMOS Test Patterns          | 26 |

|   | 6.1   | TSW3100 MultitonePattern Software           | 27 |

|   | 6.2   | TSW3100 MultitonePattern Examples           | 29 |

|   | 6.3   | TSW3100_CommSignalPattern Software          |    |

|   | 6.4   | TSW3100 CommSignalPattern Examples          |    |

|   |       |                                             |    |

#### List of Figures

| 1 | Do not Use Windows Update to Find Adapter Software     | . 8 |

|---|--------------------------------------------------------|-----|

| 2 | Install USB to Ethernet Adapter Software               | . 9 |

| 3 | USB to Ethernet Adapter Software Installation Complete | . 9 |

| 4 | Configure USB to Ethernet Connection                   | 10  |

| 5 | Specify IP Address and Subnet Mask                     | 10  |

| 6 | Choose Setup Language                                  |     |

| 7 | MATLAB Welcome Screen                                  | 11  |

| 8 | Customer Information                                   | 12  |

| 9 | Destination Folder                                     | 12  |

|   |                                                        |     |

Stratix II, ByteBlaster II, USB-Blaster are trademarks of Altera Corporation. Windows is a trademark of Microsoft Corporation. LabVIEW is a trademark of National Instruments Corporation. MATLAB is a trademark of The MathWorks, Inc.

1

| 10 | Ready to Install the Program                                                | 13 |

|----|-----------------------------------------------------------------------------|----|

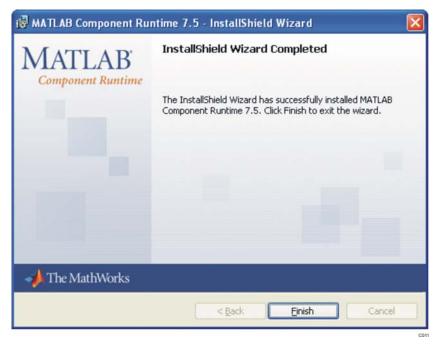

| 11 | InstallShield Wizard Completed                                              | 13 |

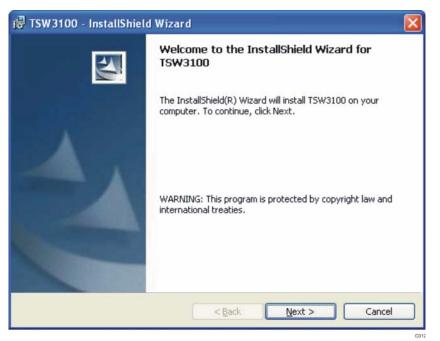

| 12 | TSW3100 Installation Welcome                                                | 14 |

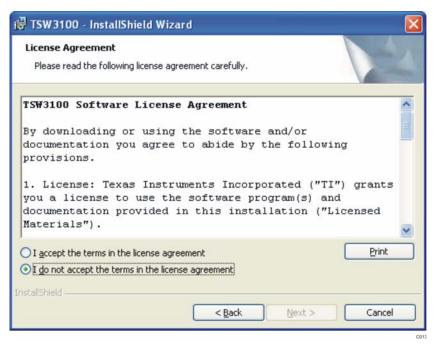

| 13 | TSW3100 License Agreement                                                   | 14 |

| 14 | Customer Information                                                        | 15 |

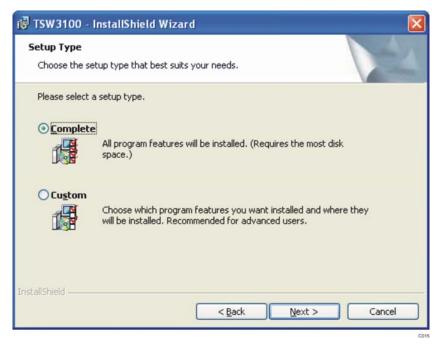

| 15 | Setup Type                                                                  | 15 |

| 16 | Ready to Install the Program                                                | 16 |

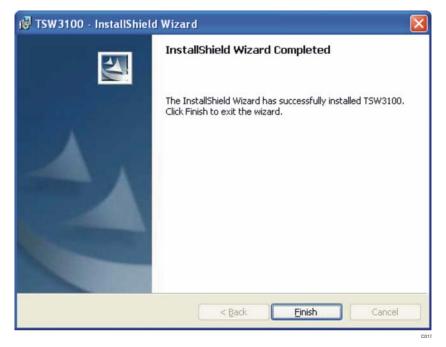

| 17 | InstallShield Wizard Completed                                              | 16 |

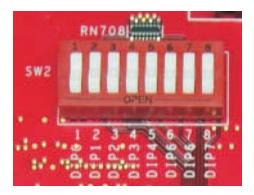

| 18 | SW2 DIP Switches                                                            | 17 |

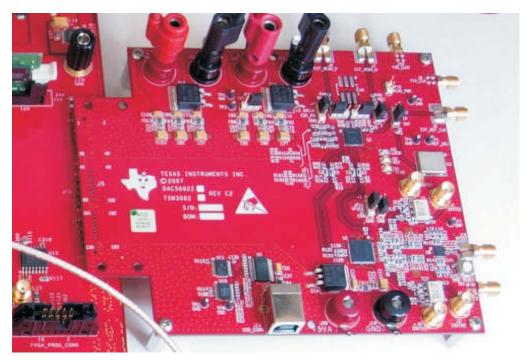

| 19 | Connection of the DAC5682Z EVM to the TSW3100                               | 19 |

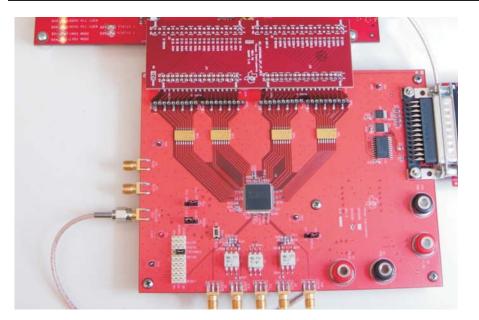

| 20 | CMOS HSDAC Connection to the TSW3100                                        | 20 |

| 21 | TSW3100_MultiTonePattern Graphical User Interface                           | 27 |

| 22 | Tone Groups Settings                                                        | 29 |

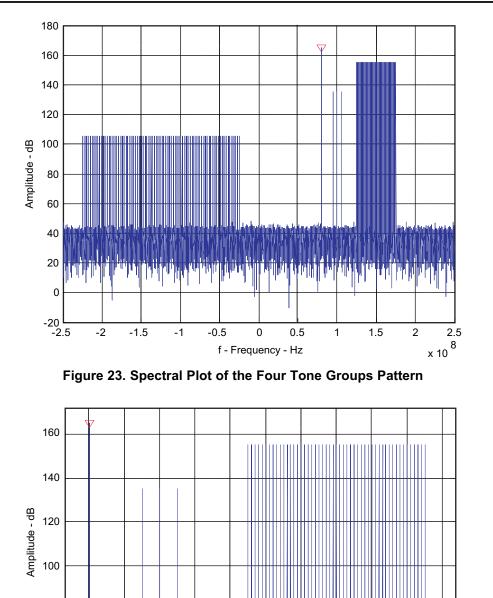

| 23 | Spectral Plot of the Four Tone Groups Pattern                               | 30 |

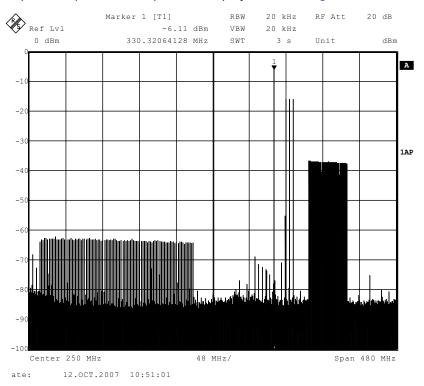

| 24 | Magnify Tone Groups 1-3 Shown in Previous Figure                            | 30 |

| 25 | DAC5682Z Output Spectrum for Four Tone Groups                               | 31 |

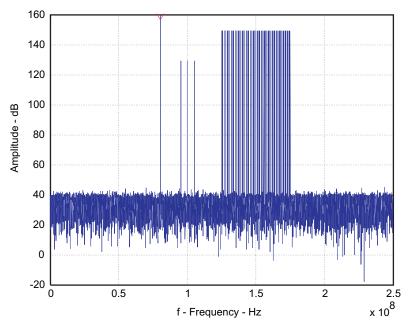

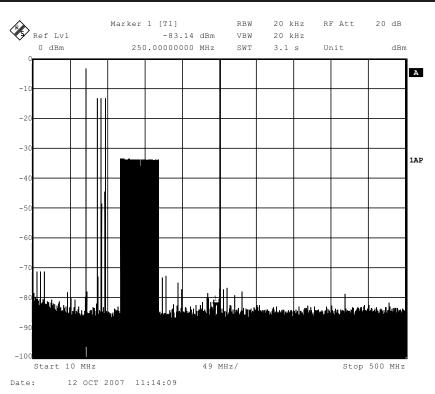

| 26 | Spectral Plot of Real IF Pattern                                            | 32 |

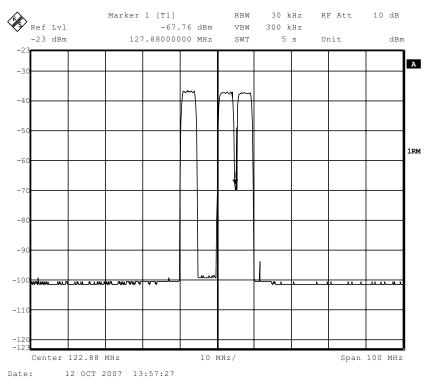

| 27 | DAC5682Z Output Spectrum for Example 2                                      | 33 |

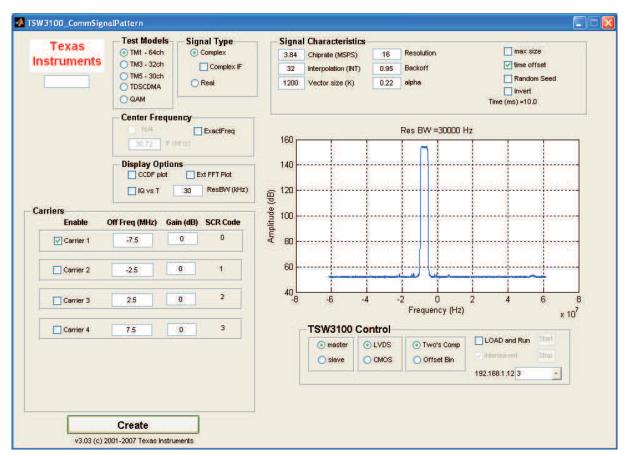

| 28 | TSW3100_CommSignalPattern Graphical User Interface                          | 34 |

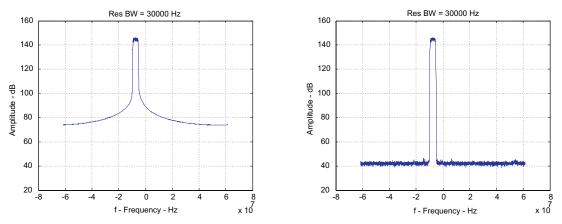

| 29 | Comparison of Using the Exact Frequency (left) vs Rounded Frequency (right) | 36 |

| 30 | Carrier Input Parameters for WCDMA TM1 Example                              | 37 |

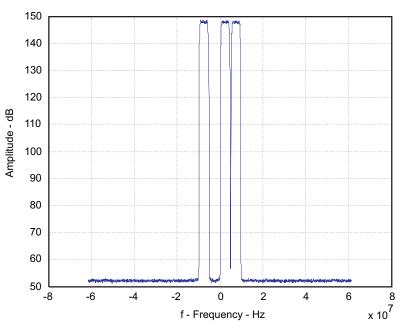

| 31 | FFT of Three Carrier WCDMA TM1 Pattern                                      | 38 |

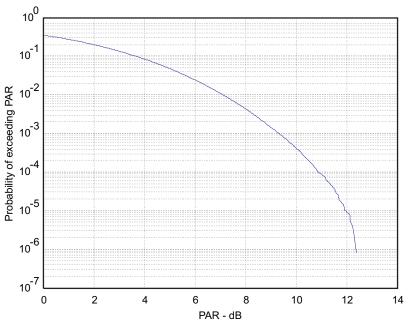

| 32 | CCDF of Three Carrier WCDMA TM1 Pattern                                     | 38 |

| 33 | DAC5687 Output Spectrum for WCDMA TM1 Example                               | 39 |

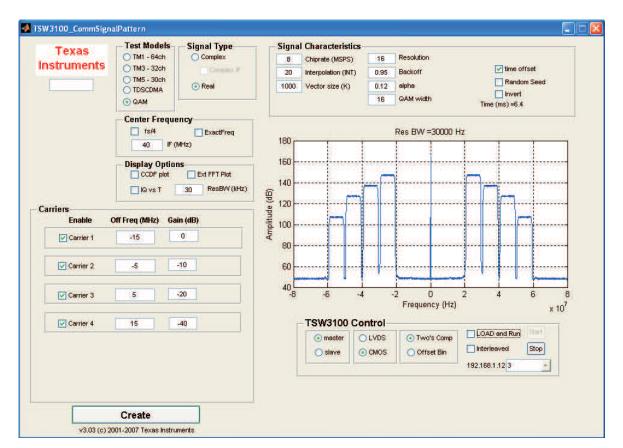

| 34 | GUI Interface for the Four Carrier QAM256 Pattern                           | 40 |

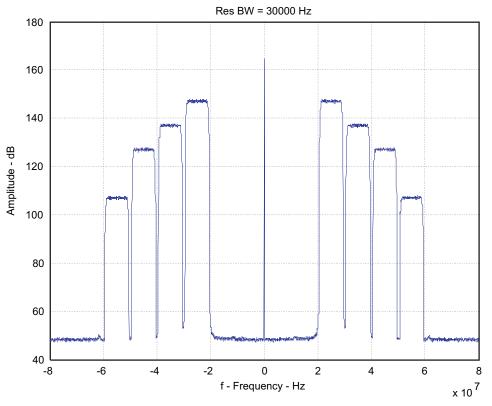

| 35 | Four Carrier QAM256 Pattern Spectral Plot                                   | 41 |

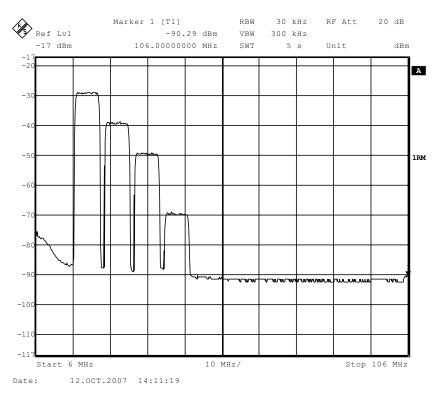

| 36 | DAC5687 Output Spectrum for Four Carrier QAM256 Pattern                     | 42 |

#### List of Tables

| Push-button and DIP Switch Functions | . 3                                                                                                                                                                                                                                           |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED Status Descriptions              | . 3                                                                                                                                                                                                                                           |

| Input and Output Connectors          | . 4                                                                                                                                                                                                                                           |

| CMOS Output Data Bus A Connector J63 | . 4                                                                                                                                                                                                                                           |

| CMOS Output Data Bus B Connector J64 | . 5                                                                                                                                                                                                                                           |

| LVDS Output Connector J74            | . 6                                                                                                                                                                                                                                           |

| IP Address Digit Selection Using SW2 | 17                                                                                                                                                                                                                                            |

| TSW3100 LEDs for LVDS Patterns       | 20                                                                                                                                                                                                                                            |

| TSW3100 LEDs for CMOS Patterns       | 21                                                                                                                                                                                                                                            |

|                                      | LED Status Descriptions<br>Input and Output Connectors<br>CMOS Output Data Bus A Connector J63<br>CMOS Output Data Bus B Connector J64<br>LVDS Output Connector J74<br>IP Address Digit Selection Using SW2<br>TSW3100 LEDs for LVDS Patterns |

## **1** Hardware Configuration

The TSW3100 EVM can be set up in a variety of configurations to accommodate a specific mode of operation. Before starting the evaluation, you should decide on the configuration and make the appropriate connections or changes. The demonstration board comes with this factory-set configuration:

- Board set to the Ethernet IP 192.168.1.123 address. This address is controlled be switch SW2, using DIP0 and DIP1 switches. (See Figure 18 and Table 7.)

- SW2 switch DIP2 set to OPEN. This switch is not currently used.

- SW2 switches DIP3-DIP7 set to OPEN. These switches are used to set the sync delay when operating two TSW3100 boards in the Master/Slave mode.

- FPGA Input Clock select jumper J50 jumper installed between pins 2-3. This directs the Field Programmable Gate Array (FPGA) to use the on-board 100 MHz oscillator. For external CLK operation, set the jumper to pins 1-2 and provide a CMOS level clock source to connector J41 (FPGA INPUT CLK).

## 1.1 Power Input Source

Use the provided 5V–6V AC-DC switching power supply to apply power to the TSW3100. The incoming power is regulated down to 0.9 V, 1.2 V, 1.8 V, 2.5 V, and 3.3 V with on-board LDO regulators to generate the necessary voltages. The input power to these regulators is controlled by SW1.

## 1.2 Output Power Regulators

The TSW3100 provides two output power sources with these default settings:

- +3.3 V @ 1 A at J10 and the return at J38.

- +1.8 V @ 1 A at J7 and the return to J39.

Both power supplies are derived using low noise LDO regulators and controlled by switch SW5. This switch is independent of the operation of the main board power switch SW1. Both LDOs are adjustable regulators and can be modified by changing one resistor. To change the output voltage of the +1.8 V supply, replace R27 with the appropriate value. To change the output voltage of the +3.3 V supply, replace R31 with the appropriate value. See the TI TPS76701 data sheet (<u>SGLS157</u>) for more information regarding these devices.

## 1.3 Switches and LEDs

The TSW3100 provides an eight-position DIP switch and four push-button switches you can use during the EVM operation. Table 1 describes the DIP switch functionality.

| Reference<br>Designator | Switch Name | Description                                                                       |  |

|-------------------------|-------------|-----------------------------------------------------------------------------------|--|

| S3                      | SYNC        | Sends a one-time SYNC pulse at the start of the test pattern.                     |  |

| S7                      | START/STOP  | Stops a test pattern that is running. When pressed again, starts the est pattern. |  |

| S8                      | SPARE       | Not used                                                                          |  |

| S9                      | FPGA CONFIG | Reconfigures the FPGA when pressed.                                               |  |

| SW2                     | DIP0        | Sets the Board Ethernet IP address <sup>(1)</sup>                                 |  |

| SW2                     | DIP1        | Sets the Board Ethernet IP address <sup>(1)</sup>                                 |  |

| SW2                     | DIP2        | Adjust SYNC when in CMOS mode (Master/Slave operation only)                       |  |

| SW2                     | DIP3-DIP7   | Adjust SYNC when in LVDS mode (Master/Slave operation only)                       |  |

Table 1. Push-button and DIP Switch Functions

<sup>(1)</sup> See Table 7 to set the TSW3100 board IP address using these switches.

Ten LEDs display the TSW3100 EVM status during its operation. Table 2 describes the meaning of each LED status.

| Reference<br>Designator | LED Name         | Description <sup>(1)</sup>                                                                                                 |  |

|-------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| D13                     | PAT GEN IDLE     | When power is applied, this LED should light, indicating the board is ready to load test pattern information.              |  |

| D14                     | PAT GEN CLK      | When pattern generator starts, this LED lights, if the required clock is present. LED is OFF during idle mode.             |  |

| D15                     | PAT GEN RUN      | hen the pattern generator starts, this LED lights. LED is OFF during idle mode.                                            |  |

| D16                     | FIFO EMPTY ERROR | N—error when loading the internal FIFO of the FPGA.                                                                        |  |

| D17                     | FIFO FULL ERROR  | N—error when unloading the internal FIFO of the FPGA.                                                                      |  |

| D18                     | LVDS PLL LOCK    | ON—indicates feedback LVDS clock present on J74. Should always be ON when using LVDS outputs with an EVM plugged into J74. |  |

<sup>(1)</sup> See Table 8 and Table 9 for LED patterns during TSW3100 operations.

| Reference<br>Designator | LED Name      | Description <sup>(1)</sup>                                                                                                 |

|-------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------|

| D19                     | DDR2 PLL LOCK | ON—indicates the presence of the FPGA clock used for the DDR2 interface. Should always be ON.                              |

| D20                     | NIOS PLL LOCK | ON-indicates the FPGA clock is locked to the input clock. Should always be ON.                                             |

| D21                     | CMOS MODE     | When pattern generator starts, this LED lights when the EVM is set for CMOS output mode. This LED is OFF during idle mode. |

| D22                     | LVDS MODE     | When pattern generator starts, this LED lights when the EVM is set for LVDS output mode. This LED is OFF during idle mode. |

## Table 2. LED Status Descriptions (continued)

# 1.4 Input and Output Connectors

Table 3 describes the input and output connectors.

| Reference<br>Designator | Connector Type                                                   | Description                                                                                          |  |

|-------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|

| J9                      | Power Connector                                                  | 5V-6V VDC input power from AC-to-DC power supply                                                     |  |

| J24                     | 240 DIMM                                                         | DDR2 dual in-line memory module connector                                                            |  |

| J13                     | CONN MAGJACK                                                     | 10/100 Ethernet Connector                                                                            |  |

| J74                     | 160 pin 0.5mm-pitch QSH-DP series<br>Samtec High Speed Connector | LVDS output data connector                                                                           |  |

| J63                     | 40 pin male header connectors                                    | Data Bus A CMOS output data                                                                          |  |

| J64                     | 40 pin male header connectors                                    | Data Bus B CMOS output data                                                                          |  |

| J55                     | 10 pin male header                                               | JTAG interface to FPGA and serial PROM                                                               |  |

| J44                     | 10 pin male header                                               | JTAG interface to FPGA and FLASH                                                                     |  |

| J10                     | Banana Jack                                                      | +3.3 V out @ 1 A                                                                                     |  |

| J38                     | Banana Jack                                                      | +3.3 V Return                                                                                        |  |

| J7                      | Banana Jack                                                      | +1.8 V out @ 1 A                                                                                     |  |

| J39                     | Banana Jack                                                      | +1.8 V Return                                                                                        |  |

| J47                     | SMA                                                              | Sync Out (Master Mode only)                                                                          |  |

| J48                     | SMA                                                              | Sync In. Used only in Slave Mode.                                                                    |  |

| J73                     | SMA                                                              | CMOS CLK. Required when board is generating CMOS output data.                                        |  |

| J45                     | SMA                                                              | CLK OUT. Spare output clock. Same clock used by the FPGA.                                            |  |

| J41                     | SMA                                                              | FPGA INPUT CLK. Required when jumper J50 is set to external clock mode (1-2).                        |  |

| J49                     | SMA                                                              | Spare IO. Spare input or output if assigned to FPGA firmware. Default firmware does not assign this. |  |

#### **Table 3. Input and Output Connectors**

## 1.4.1 Output Data Connectors

The TSW3100 provides CMOS outputs to drive existing TI HSDAC EVMs. The CMOS outputs use two connectors which interface directly to the TI DAC5687 and DAC5688 EVMs when using the provided adapter board. Table 4 and Table 5 define the pinout of CMOS output connectors J63 and J64.

| Pin | Description            | Pin | Description     |  |

|-----|------------------------|-----|-----------------|--|

| 1   | CMOS Data Bit 15 (MSB) | 21  | CMOS Data Bit 5 |  |

| 2   | GND                    | 22  | GND             |  |

| 3   | CMOS Data Bit 14       | 23  | CMOS Data Bit 4 |  |

| 4   | GND                    | 24  | GND             |  |

| Table 4. CMOS Output Data Bu | us A Connector J63 |

|------------------------------|--------------------|

|------------------------------|--------------------|

| Pin | Description      | Pin | Description           |

|-----|------------------|-----|-----------------------|

| 5   | CMOS Data Bit 13 | 25  | CMOS Data Bit 3       |

| 6   | GND              | 26  | GND                   |

| 7   | CMOS Data Bit 12 | 27  | CMOS Data Bit 2       |

| 8   | GND              | 28  | GND                   |

| 9   | CMOS Data Bit 11 | 29  | CMOS Data Bit 1       |

| 10  | GND              | 30  | GND                   |

| 11  | CMOS Data Bit 10 | 31  | CMOS Data Bit 0 (LSB) |

| 12  | GND              | 32  | GND                   |

| 13  | CMOS Data Bit 9  | 33  | Sync                  |

| 14  | GND              | 34  | GND                   |

| 15  | CMOS Data Bit 8  | 35  | Spare                 |

| 16  | GND              | 36  | GND                   |

| 17  | CMOS Data Bit 7  | 37  | Spare                 |

| 18  | GND              | 38  | GND                   |

| 19  | CMOS Data Bit 6  | 39  | Spare                 |

| 20  | GND              | 40  | GND                   |

#### Table 4. CMOS Output Data Bus A Connector J63 (continued)

Table 5. CMOS Output Data Bus B Connector J64

| Pin | Description            | Pin | Description           |

|-----|------------------------|-----|-----------------------|

| 1   | CMOS Data Bit 15 (MSB) | 21  | CMOS Data Bit 5       |

| 2   | GND                    | 22  | GND                   |

| 3   | CMOS Data Bit 14       | 23  | CMOS Data Bit 4       |

| 4   | GND                    | 24  | GND                   |

| 5   | CMOS Data Bit 13       | 25  | CMOS Data Bit 3       |

| 6   | GND                    | 26  | GND                   |

| 7   | CMOS Data Bit 12       | 27  | CMOS Data Bit 2       |

| 8   | GND                    | 28  | GND                   |

| 9   | CMOS Data Bit 11       | 29  | CMOS Data Bit 1       |

| 10  | GND                    | 30  | GND                   |

| 11  | CMOS Data Bit 10       | 31  | CMOS Data Bit 0 (LSB) |

| 12  | GND                    | 32  | GND                   |

| 13  | CMOS Data Bit 9        | 33  | TXENABLE              |

| 14  | GND                    | 34  | GND                   |

| 15  | CMOS Data Bit 8        | 35  | Spare                 |

| 16  | GND                    | 36  | GND                   |

| 17  | CMOS Data Bit 7        | 37  | Spare                 |

| 18  | GND                    | 38  | GND                   |

| 19  | CMOS Data Bit 6        | 39  | Spare                 |

| 20  | GND                    | 40  | GND                   |

The TSW3100 provides LVDS level outputs to drive existing TI HSDAC EVMs. The LVDS outputs use a high speed, 0.5 mm-pitch connector from Samtec, which interfaces directly to the TI DAC5682 EVM. Table 6 defines the pinout for the LVDS Output Connector J74.

# Table 6. LVDS Output Connector J74

| Pin | Description | Pin | Description |

|-----|-------------|-----|-------------|

| 1   | +1.8VD      | 21  |             |

| 2   | +1.8VD      | 22  |             |

| 3   | +1.8VD      | 23  |             |

| 4   | +1.8VD      | 24  |             |

| 5   |             | 25  |             |

| 6   | GND         | 26  | DSP3        |

| 7   |             | 27  |             |

| 8   | GND         | 28  | DSP4        |

| 9   |             | 29  |             |

| 10  | GND         | 30  |             |

| 11  |             | 31  |             |

| 12  | GND         | 32  |             |

| 13  | +3.3VD      | 33  |             |

| 14  | +3.3VD      | 34  | DSP5        |

| 15  | +3.3VD      | 35  |             |

| 16  | +3.3VD      | 36  | DSP6        |

| 17  | DSP7        | 37  |             |

| 18  | DSP1        | 38  |             |

| 19  | DSP8        | 39  |             |

| 20  | DSP2        | 40  |             |

| 41  |             | 61  | DA13N       |

| 42  |             | 62  | DB13N       |

| 43  |             | 63  |             |

| 44  |             | 64  |             |

| 45  |             | 65  | DA12P       |

| 46  |             | 66  | DB12P       |

| 47  | DA15P       | 67  | DA12N       |

| 48  | DB15P       | 68  | DB12N       |

| 49  | DA15N       | 69  |             |

| 50  | DB15N       | 70  |             |

| 51  |             | 71  | DA11P       |

| 52  |             | 72  | DB11P       |

| 53  | DA14P       | 73  | DA11N       |

| 54  | DB14P       | 74  | DB11N       |

| 55  | DA14N       | 75  |             |

| 56  | DB14N       | 76  |             |

| 57  |             | 77  | DA10P       |

| 58  |             | 78  | DB10P       |

| 59  | DA13P       | 79  | DA10N       |

| 60  | DB13P       | 80  | DB10N       |

| 81  |             | 101 | DA7P        |

| 82  |             | 102 | DB7P        |

| 83  | DA9P        | 103 | DA7N        |

| 84  | DB9P        | 104 | DB7N        |

| 85  | DA9N        | 105 |             |

| 86  | DB9N        | 106 |             |

| Pin | Description | Pin | Description |   |

|-----|-------------|-----|-------------|---|

| 87  |             | 107 | DA6P        |   |

| 88  |             | 108 | DB6P        |   |

| 89  | DA8P        | 109 | DA6N        |   |

| 90  | DB8P        | 110 | DB6N        |   |

| 91  | DA8N        | 111 |             |   |

| 92  | DB8N        | 112 |             |   |

| 93  |             | 113 | DA5P        |   |

| 94  |             | 114 | DB5P        |   |

| 95  | DCLKP       | 115 | DA5N        |   |

| 96  | FPGA_CLKP   | 116 | DB5N        |   |

| 97  | DCLKN       | 117 |             |   |

| 98  | FPGA_CLKN   | 118 |             |   |

| 99  |             | 119 | DA4P        |   |

| 100 |             | 120 | DB4P        |   |

| 121 | DA4N        | 141 |             |   |

| 122 | DB4N        | 142 |             |   |

| 123 |             | 143 | DA0P        |   |

| 124 |             | 144 | DB0P        |   |

| 125 | DA3P        | 145 | DAON        |   |

| 126 | DB3P        | 146 | DB0N        | - |

| 127 | DA3N        | 147 |             | - |

| 128 | DB3N        | 148 |             |   |

| 129 |             | 149 |             | - |

| 130 |             | 150 | DBCLKP      |   |

| 131 | DA2P        | 151 |             |   |

| 132 | DB2P        | 152 | DBCLKN      |   |

| 133 | DA2N        | 153 |             |   |

| 134 | DB2N        | 154 |             |   |

| 135 |             | 155 | SYNCP       |   |

| 136 |             | 156 |             |   |

| 137 | DA1P        | 157 | SYNCN       |   |

| 138 | DB1P        | 158 |             |   |

| 139 | DA1N        | 159 |             |   |

| 140 | DB1N        | 160 |             |   |

| 161 | GND         | 167 | GND         |   |

| 162 | GND         | 168 | GND         |   |

| 163 | GND         | 169 | GND         |   |

| 164 | GND         | 170 | GND         |   |

| 165 | GND         | 171 | GND         | - |

| 166 | GND         | 172 | GND         |   |

## Table 6. LVDS Output Connector J74 (continued)

#### 1.4.2 JTAG Connectors

Two JTAG headers (10-pin key shrouded header J55 and J44) are provided for configuring the Stratix II<sup>™</sup> FPGA and the FLASH memory device. The programming is done through using an Altera ByteBlaster II<sup>™</sup> or USB-Blaster<sup>™</sup> cable. The board comes with operational firmware stored in a serial PROM device that loads the FPGA at power up. You do not need to download any firmware.

#### 1.4.3 Ethernet Connector

The TSW3100 provides a 10/100 Ethernet interface for Ethernet connections up to 100 Mbps. The reference designator for this interface is J13.

#### 2 Software Installation

TI provides several software tools to help you use the TSW3100 for evaluation of TI DACs. The user can follow the interface protocol discussed in Section 4.2.

#### 2.1 USB to Ethernet Adapter Installation

The USB interface adapter is provided to allow an additional, dedicated PC IP address to connect to the fixed TSW3100 IP address. To install this adapter:

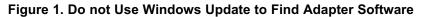

1. Connect the included USB to Ethernet adapter to a spare USB port of the host PC. The Windows *Found New Hardware Wizard* (Figure 1) displays. If this does not happen, ensure the cable is connected properly. Select the *No, not this time* option button and click *Next*.

Insert the USB to Ethernet Adapter installation CD. The installation should start automatically (Figure 2). When it starts, select the *Install the software automatically (Recommended)* option and click *Next*.

Figure 2. Install USB to Ethernet Adapter Software

3. Wait for the Found New Hardware Wizard to complete (Figure 3). Press Finish.

Figure 3. USB to Ethernet Adapter Software Installation Complete

4. Restart the host PC.

# 2.2 Configure the USB to Ethernet network

- 1. Select the Windows Start menu, select the Control Panel, and choose the Network Connections item.

- 2. Double-click the *Local Area Connection* whose device name is *ASIX AX88772 USB2.0 to Fast Ethernet Adapter.* The *Local Area Connection Properties* dialog (Figure 4) displays.

|                                                             | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Connect using:                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |

| ASIX AX88772 USB2.0 to Fast Ether Configure                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |

| This connection use                                         | s the following items:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |

|                                                             | tocol (IEEE 802.1x) v3.0.0<br>tocol (IEEE 802.1x) v2.3.0<br>stocol (TCP/IP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |

| <                                                           | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ) ))            |

| Install                                                     | Uninstall                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Properties      |

| Description                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |

| Description                                                 | Company of the second se | and The default |

| Transmission Con<br>wide area network                       | trol Protocol/Internet Pro<br>k protocol that provides c<br>erconnected networks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |

| Transmission Con<br>wide area network<br>across diverse int | k protocol that provides c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ommunication    |

Figure 4. Configure USB to Ethernet Connection

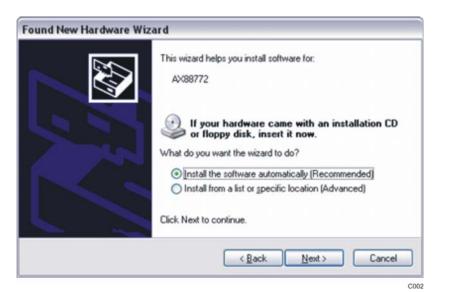

- 3. Double-click the *Internet Protocol (TCP/IP)* item (Figure 4) found under the *General* dialog tab and listed in the *This Connection uses the following items* selection list.

- 4. Select the *Use the following IP address* option (Figure 5). Type 192.168.1.1 for the *IP address* and 255.255.255.0 for the *Subnet Mask*.

| tomatically if your network supports<br>o ask your network administrator for<br>cally |

|---------------------------------------------------------------------------------------|

| ally                                                                                  |

|                                                                                       |

|                                                                                       |

| 192.168.1.1                                                                           |

| 255 . 255 . 255 . 0                                                                   |

|                                                                                       |

| omatically<br>ddresses:                                                               |

| 100 100 100 100 100 100 100 100 100 100                                               |

|                                                                                       |

| Advanced                                                                              |

| OK Cano                                                                               |

|                                                                                       |

5. Click *OK* for both the Internet Protocol (TCP/IP) Properties and Local Area Connection Properties dialogs.

# 2.3 Installing the MATLAB Runtime Engine

This section helps you install the MATLAB Runtime engine which is used to run the provide MATLAB executable code.

1. Double-click on the *MCRInstaller.exe* file located on the TSW3100 installation CD. The Choose Setup Language (Figure 6) displays. Click *OK* for English (United States).

Figure 6. Choose Setup Language

2. When the MATLAB Component Runtime 7.5 screen (Figure 7) displays, click Next.

| 🛃 MATLAB Component Ru       | ntime 7.5 - InstallShield Wizard 🛛 🛛 🔀                                                                                         |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| MATLAB<br>Component Runtime | Welcome to the InstallShield Wizard for<br>MATLAB Component Runtime 7.5                                                        |

|                             | The InstallShield(R) Wizard will install MATLAB Component<br>Runtime 7.5 on your computer. To continue, click Next.            |

|                             | WARNING: This program is protected by copyright law and<br>international treaties. Copyright 1984-2006, The MathWorks,<br>Inc. |

| 📣 The MathWorks             |                                                                                                                                |

|                             | < <u>Back</u> <u>N</u> ext > Cancel                                                                                            |

Figure 7. MATLAB Welcome Screen

3. For the *Customer Information* (Figure 8) screen, specify the *User Name*, *Organization*, select the desired user option button, and click *Next*.

| 🖟 MATLAB Component Runtime 7.5 - InstallShield Wizard 🛛 🛛 🔀                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------|

| Customer Information                                                                                                          |

| Please enter your information.                                                                                                |

| User Name:                                                                                                                    |

| TI User                                                                                                                       |

| Organization:                                                                                                                 |

| Texas Instruments, Inc                                                                                                        |

| Install this application for:<br><ul> <li>Anyone who uses this computer (all users)</li> <li>Only for me (TI User)</li> </ul> |

| InstallShield                                                                                                                 |

Figure 8. Customer Information

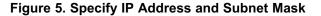

4. When the *Destination Folder* screen (Figure 9) displays, click *Next* to install the MATLAB software in the default directory.

**Figure 9. Destination Folder**

5. When the *Ready to Install the Program* screen (Figure 10) displays, click *Install* to begin the installation. The installation lasts approximately five minutes.

| 🖟 MATLAB Component Runtime 7.5 - InstallShield Wizard 🛛 🛛 🔀                                                     |

|-----------------------------------------------------------------------------------------------------------------|

| Ready to Install the Program                                                                                    |

| The wizard is ready to begin installation.                                                                      |

| Click Install to begin the installation.                                                                        |

| If you want to review or change any of your installation settings, click Back. Click Cancel to exit the wizard. |

| InstallShield                                                                                                   |

Figure 10. Ready to Install the Program

6. Click Finish once the InstallShield Wizard Completed screen (Figure 11) displays.

Figure 11. InstallShield Wizard Completed

## 2.4 Installing the TSW3100 Application Software

1. Double-click on the *TSW3100Installer.exe* file located on the TSW3100EVM installation CD. The TSW3100 Installation Wizard (Figure 12) displays. Click *Next*.

Figure 12. TSW3100 Installation Welcome

2. When the License Agreement (Figure 13) displays, select the *I accept the terms in the License agreement* option and click *Next* to accept the TSW3100 Software License Agreement.

Figure 13. TSW3100 License Agreement

3. On the Customer Information (Figure 14) display, provide User Name, Organization information, and

| Customer Information                                                                            |  |

|-------------------------------------------------------------------------------------------------|--|

| Please enter your information.                                                                  |  |

| User Name:                                                                                      |  |

| TI User                                                                                         |  |

| Organization:                                                                                   |  |

| TI                                                                                              |  |

| Install this application for:                                                                   |  |

| <ul> <li>Anyone who uses this computer (all users)</li> <li>Only for me (Eric Zhang)</li> </ul> |  |

select the appropriate Install this Application for option. Click Next.

**Figure 14. Customer Information**

4. On the Setup Type (Figure 15) display, select the Complete Setup Type option and click Next.

Figure 15. Setup Type

5. On the Ready to Install the Program (Figure 16) display, click *Install*. The installation takes between one and three minutes to complete.

| 记 TSW3100 - InstallShield Wizard                                           |                                                   |

|----------------------------------------------------------------------------|---------------------------------------------------|

| Ready to Install the Program<br>The wizard is ready to begin installation. |                                                   |

| Click Install to begin the installation.                                   |                                                   |

| If you want to review or change any of your i exit the wizard.             | nstallation settings, click Back. Click Cancel to |

| InstallShield                                                              | < Back Install Cancel                             |

Figure 16. Ready to Install the Program

6. Click Finish once the InstallShield Wizard Completed screen (Figure 17) displays.

Figure 17. InstallShield Wizard Completed

## 2.5 Starting the TSW3100 Application Software

The TSW3100 software is now ready to use. To start the application programs, click the Windows menu sequence start  $\rightarrow$  All Programs  $\rightarrow$  Texas Instruments  $\rightarrow$  TWS3100Install\_IS12. You can select to display the application interface for the *TSW3100\_CommSignalPattern.exe* (Section 6.3) software or the *TSW3100\_MultiTonePattern.exe* (Section 6.1) software.

## 3 Apply Power to TSW3100 and Connect to a Host

To power the TSW3100, connect the 5–6 V power supply to J9. Move switch SW1 to the ON position. The four LEDs D3-D6 should now light. In addition, D13, D19 and D20 should also light.

Now, connect the TSW3100 Ethernet connector with a crossover cable to the PC or USB Ethernet adapter. Within approximately 5 seconds, the green Ethernet connector should also light, indicating a connection to the host (usually PC).

## 4 Host Interface

The TSW3100 uses simple interface protocols with TCP/IP over Ethernet with control and data transfer by Trivial FIle Transfer Protocol (TFTP). The protocols are host operating system agnostic (Windows, Linux, and so forth), although all examples and software provided by Texas Instruments are developed for Windows™ XP.

## 4.1 TSW3100 IP Address

The TSW3100 has a fixed IP address: 192.168.1.12x. The final digit x is defined by the DIP0 and DIP1 switch positions (Table 7) on SW2 (Figure 18) whenever power is applied or the FPGA is reconfigured.

Figure 18. SW2 DIP Switches

| · · · · · · · · · · · · · · · · · · · |               |                       |

|---------------------------------------|---------------|-----------------------|

| DIP0 Position                         | DIP1 Position | IP Address            |

| Closed                                | Closed        | 192.168.1.12 <b>0</b> |

| Closed                                | Open          | 192.168.1.12 <b>1</b> |

| Open                                  | Closed        | 192.168.1.12 <b>2</b> |

| Open                                  | Open          | 192.168.1.12 <b>3</b> |

For convenience, a USB to Ethernet adapter is provided for the host PC to maintain a dynamic IP address allocation and still connect to the TSW3100 using a separate, fixed IP address. See installation instructions for the USB Ethernet adapter found in Section 2.1.

#### 4.2 TSW3100 Control Files

The TSW3100 is controlled by transferring short files with four 32-bit control words. The content of these control words:

```

Word 1 - Function code

Bit 0 - Off

Turns off pattern generator

Bit 1 - Error reset

Bit 2 - Vector write

Start writing pattern vector to TSW3100

Bit 3 - Reserved

Bit 4 - Pattern gen master cmos start

Start CMOS pattern output in Master mode

Bit 5 - Pattern gen master lvds start

Start LVDS pattern output in Master mode

Bit 6 - Pattern gen slave cmos start

Start CMOS pattern output in Slave mode

Bit7 - Pattern gen slave lvds start

Start LVDS pattern output in Slave mode

Bit8-Bit31 Not used

Word 2 - Intro vector number

Starting vector number during 1st pass

through pattern (defaults to zero)

Word 3 - Start vector number

Vector number during 2nd and later passes through

pattern (defaults to zero)

Word 4 - Finish vector number

End vector for the pattern, which returns to

Start vector number

```

Words 2–4 and the data pattern must be a multiple of 4 vectors for LVDS output.

## 4.3 TSW3100 Data Pattern Format

The TSW3100 data pattern for the LVDS output consists of 16-bit little-endian words in a sequence representing the 16 differential outputs. Note, the Low Voltage Differential Signaling (LVDS) SYNC and DATA CLK signals are generated in firmware and are not stored in memory. The TSW3100 data pattern for Complementary Metal Oxide Semiconductor (CMOS) outputs uses 36-bits of a 64-bit little-Endian word, with the final 28-bits set to zero.

These data files are easily generated with programs such as MATLAB<sup>™</sup> or LabVIEW<sup>™</sup>, with MATLAB functions described in Section 5.

## 4.4 TSW3100 Operation Sequence

The TSW3100 operation consists of several file transfers to load and start a pattern. The basic steps are (assuming an IP address of 192.168.1.123):

1. Control off

2. Vector Write Start

tftp -i 192.168.1.123 put control\_vwn /tmp/control control\_vmn is a file containing the 32-bit words: 0x 00000002 00000000 00000000 00000000

3. Data Vector Pattern

The data vector pattern must be transferred in files with sizes less than 5 MBytes, which equals 2.5M Vectors for LVDS output or 1.25Mvectors for CMOS outputs. Larger patterns are transferred in multiple steps using this sequence:

(a) Each file <5MBytes is first transferred to the TSW3100 processor memory.

tftp -i 192.168.1.123 put data\_pattern.bin /tmp/vector

(b) Transfer a **ready\_rx** file to indicate that the processor should transfer the pattern from the processor memory to the pattern memory. The ready\_rx file is any non-zero file size. We use a file contain the 32-bit word: 0x 20090120

tftp -i 192.168.1.123 put ready\_rx /tmp/ready\_rx

(c) We recommend generating a pause of 0.5 seconds per Mbyte, to allow the TSW3100 processor to transfer the pattern to pattern memory.

4. Control Pattern Generator Start

tftp -i 192.168.1.120 put control\_file /tmp/control The TSW3100 pattern is started by the transfer of the control file words shown in Section 4.2 .

# 4.5 TSW3100 Connection to LVDS HSDAC EVM

For an LVDS output to a TI LVDS interface high-speed DAC EVM (DAC5682Z EVM), connect the DAC EVM to connector J74 (see Figure 19). This connection provides the 16 LVDS differential data bits, an LVDS DATA CLK at the data rate, and the LVDS SYNC signal to the DAC EVM. On the same connector, the high speed DAC EVM provides a clock to the TSW3100 to clock the output pattern. This clock must be at 1/8<sup>th</sup> the data rate of the LVDS data, or 1/4<sup>th</sup> the DATA CLK frequency, and have a minimum frequency of 25 MHz, for a minimum LVDS data rate of 200 MHz.

Figure 19. Connection of the DAC5682Z EVM to the TSW3100

When power is applied, LEDs D13 (PATT GEN IDLE), D19 (DDR2 PLL LOCK) and D20 (NIOS PLL LOCK) should light. When an LVDS clock signal is provided on connector J74, D18 (LVDS PLL LOCK) should light.

After the LVDS pattern starts, using the sequence in Section 4.4, LEDs D14 (PATT GEN CLK), D15 (PATT GEN RUN), and D24 (LVDS MODE) should light (Table 8).

| LED Name | Power Applied     | LVDS Pattern Starts |

|----------|-------------------|---------------------|

| D13      | ON                | ON                  |

| D14      |                   | ON                  |

| D15      |                   | ON                  |

| D18      | ON (clock signal) | ON                  |

| D19      | ON                | ON                  |

| D20      | ON                | ON                  |

| D24      |                   | ON                  |

#### Table 8. TSW3100 LEDs for LVDS Patterns

# 4.6 TSW3100 Connection to CMOS HSDAC EVMs

For CMOS output to a TI CMOS interface high speed DAC (Figure 20) EVM (DAC5688 EVM), connect the DAC EVM to connectors J63 and J64 using the provided adapter PCB. This connection provides the 32 LVCMOS (3.3V) data bits to the DAC EVM. A clock at the CMOS output data rate must be provided to SMA connector J73 (CMOS CLK). This clock has a minimum frequency of 25 MHz, for a minimum CMOS data rate of 25 MHz. When using existing TI HSDAC EVMs, the TSW3100 CMOS CLK can be provided as follows:

- TI HSDAC EVMs (DAC5687EVM, DAC5688EVM or TSW3003) using external clock mode Use the PLL LOCK output SMA.

- TI HSDAC EVMs that include the CDCM7005 clock buffer using PLL Clock mode Use a spare CDCM7005 clock buffer output at the DAC data rate.

- Other TI HSDAC EVMs Provide two synchronous clock sources or split an external clock source to provide a clock for both the DAC and TSW3100.

- **Note:** The user must verify the timing of the DAC clock relative to the data to assure setup and hold times are met. These may require additional delay between the DAC EVM and TSW3100 clocks (easily accomplished by adding cable length).

Figure 20. CMOS HSDAC Connection to the TSW3100

When power is applied, LEDs D13 (PATT GEN IDLE), D19 (DDR2 PLL LOCK) and D20 (NIOS PLL LOCK) should light. There is no LED indication for the presence of the CMOS CLK.

#### Example MATLAB Functions for TSW3100 Control

After the CMOS pattern starts using the sequence in Section 4.4, LEDs D14 (PATT GEN CLK), D15 (PATT GEN RUN) and D21 (CMOS MODE) should light (Table 9).

| LED Name | Power Applied | <b>CMOS Pattern Starts</b> |

|----------|---------------|----------------------------|

| D13      | ON            | ON                         |

| D14      |               | ON                         |

| D15      |               | ON                         |

| D19      | ON            | ON                         |

| D20      | ON            | ON                         |

| D21      |               | ON                         |

#### Table 9. TSW3100 LEDs for CMOS Patterns

# 4.7 TSW3100 Master/Slave Operation

The TSW3100 includes the ability to synchronize multiple boards using a master/slave synchronization, However, this mode is not documented.

## 5 Example MATLAB Functions for TSW3100 Control

Texas Instruments provides several functions in MATLAB for generation of pattern and control files and interfacing to the TW3100. These functions are provided as \*.m files with the TSW3100.

These functions include:

- Section 5.1 LVDS Pattern File Generation

- Section 5.2 CMOS Pattern File Generation

- Section 5.3 Pattern File Loading to the TSW3100

- Section 5.4 Running the TSW3100

#### 5.1 LVDS Pattern File Generation

The function **TSW3100writer\_lvds** is used to generate the 16-bit words for the LVDS pattern. **File\_Name** is a text string with file path and name for the output pattern file. The input data is assumed to be real or complex 16-bit integers, scaled between -32768 and 32767. The input variable **twos\_or\_offset** is a string that must start with a **t** (twos-compliment) or **o** (offset binary) to signify the format of the output pattern. The input variable **complex\_or\_real** is a string that must start with **c** or **r** (can be longer) to signify if the input vector is real or complex. The function returns the length of the pattern, which would be double the length of the input data for complex data since the output is interleaved complex.

```

function vector_length=TSW3100writer_lvds(File_Name, data, twos_or_offset, complex or real);

% TSW3100writerfast complex(File Name, data, twos or offset)

% File_Name = text string with file path and name

% data = real or complex integer data scaled between

ŝ

-32768 (full scale negative) and

2

32767 (full scale positive)

% twos or offset = the matlab string 'two' for twos complement and

'off' for offset binary

0

% writes in little endian for TSW3100 LVDS output format

% 16-bits per vector, two vectors used for interleaved complex signal

if complex or real(1:1) == 'c'

%data is complex so interleave real and imaginary into array to write

if twos_or_offset(1:1) == 't'

data interleaved(1:2:2*length(data))=real(data);

data interleaved(2:2:2*length(data))=imag(data);

elseif twos or offset(1:1) == 'o

data_interleaved(1:2:2*length(data))=real(data)+32768;

data_interleaved(2:2:2*length(data))=imag(data)+32768;

else

error_msg = 'twos_or_offset must be string two... or off...'

end

elseif complex_or_real(1:1) == 'r'

```

Example MATLAB Functions for TSW3100 Control

```

%data is real so just copy into array to write

if twos or offset(1) == 't'

data interleaved=data;

elseif twos or offset(1) == 'o'

data interleaved=data+32768;

else

error_msg = 'twos_or_offset must be string starting with t or o'

end

else

error_msg = 'twos_or_offset must be string starting with t or o'

end

vector length=length(data interleaved);

% write the little endian binary file

fp = fopen(File Name, 'wb');

fwrite(fp,data interleaved,'ubit16')

fclose(fp);

```

## 5.2 CMOS Pattern File Generation

The function **TSW3100writer\_cmos** is used to generate the 64-bit words for the CMOS pattern. **File\_Name** is a text string with file path and name for the output pattern file. The **data** is assumed to be real or complex 16-bit integers, scaled between -32768 and 32767. The input variable **twos\_or\_offset** is a string that must start with a **t** (twos-compliment) or **o** (offset binary) to signify the format of the output pattern. The function returns the length of the pattern.

```

function vector length=TSW3100writer cmos(File Name, data, twos or offset);

% TSW3100writerfast cmos complex twos(File Name, data, twos or offset)

% File_Name = text string with file path and name

% data = complex integer data scaled between

-32768 (full scale negative) and

ŝ

8

32767 (full scale positive)

% twos or offset = a matlab string starting with 't' for twos complement and

'o' for offset binary

ŝ

% writes in little endian for TSW3100 CMOS output format

% 64-bits per vector, I = 16 MSBs, Q = next 16 bits, bits 33-36 are for

% the extra 4 sync signals (not used here)

vector length=length(data);

if twos or offset(1:1) == 't'

% interleave the complex data with odd being real

data interleaved(1:4:4*length(data))=real(data);

data interleaved(2:4:4*length(data))=imag(data);

data_interleaved(3:4:4*length(data))=0;

data interleaved(4:4:4*length(data))=0;

elseif twos_or_offset(1:1) == 'o'

data interleaved(1:4:4*length(data))=real(data)+32768;

data_interleaved(2:4:4*length(data))=imag(data)+32768;

data_interleaved(3:4:4*length(data))=0;

data interleaved(4:4:4*length(data))=0;

else

error_msg = 'twos_or_offset must be string starting with t or o'

end

% write the little endian binary file

fp = fopen(File Name, 'wb');

fwrite(fp,data interleaved,'ubit16')

fclose(fp);

```

## 5.3 Pattern File Loading to TSW3100

The function **TSW3100\_vectorwrite\_load** is used to process a complete MATLAB data pattern and does the complete procedure to load it into the TSW3100 pattern memory. As needed, it breaks a large data pattern into smaller pattern segments to transfer sequentially. The input arguments are the data pattern **data**, **lvds\_or\_cmos** (a string starting with either **I** or **c**) indicating an LVDS or CMOS pattern, **twos\_or\_offset** (a string starting with either **t** or **c**), and **IPdigit**, the last digit of the IP address 192.168.1.12x.

The output argument is the data pattern length, which can be 2x the input pattern length for LVDS interleaved complex data.

This function includes two sub-functions:

- TSW3100\_vectorwrite\_end—transfers each pattern segment to TSW3100 process memory

- transfer\_file—transfers the segment from processor memory to pattern memory

In addition, the functions TSW3100writer\_lvds (Section 5.1) and TSW3100writer\_cmos (Section 5.2). The function TSW3100\_vectorwrite\_load performs these operations:

- 1. Check if input data is complex

- 2. Calculate the maximum pattern segment length that can be transferred

- 3. If less them the maximum length, transfer once

- 4. If more than the maximum length, break into segments and transfer each sequentially

Example MATLAB Functions for TSW3100 Control

```

Function vector length = TSW3100 vectorwrite load (data, lvds or cmos, twos or offset, IPdigit)

% TSW3100 vectorwrite load(data, lvds or cmos, twos or offset, IPdigit)

% data = real or complex integer data scaled between

ŝ

-32768 (full scale negative) and

32767 (full scale positive)

8

% lvds or cmos = the matlab string starting with 'l' for twos complement and

'c' for offset binary

ŝ

% twos or offset = the matlab string starting with 't' for twos complement and

'o' for offset binary

%automatically checks of the data vector is complex or real

if max(abs(imag(data)))>0

complex = 2;

complex or real = 'c'

else

complex = 1;

complex_or_real = 'r'

end

% finds the # of pattern vectors that result in 5MByte file which is

% the maximum for a single

if lvds or cmos(1) == 'l'

maxlength = 2500*1024/complex;

vector length=complex*length(data);

else

maxlength = 2500 * 1024/4;

vector length=length(data);

end

$convert matlab vector to binary format to load to pattern generator

if lvds or cmos(1) == 'l'

%calculate the # of loads needed to transfer the data

numloads=ceil(length(data)/maxlength);

if numloads == 1

%Pattern is less than the maximum pattern size, so we can

%transfer all at once

v length=TSW3100writer lvds('tsw3100 tempvector.bin', data, twos or offset,

complex or real);

transfer file(IPdigit);

TSW3100_vectorwrite_end(v_length,lvds_or_cmos,IPdigit);

else

%Pattern is more than the maximum pattern size, so we must

%break the pattern into separate files and load sequentially

%sequence through the # of loads - 1 at maximum size

for index = 1:numloads-1

%calculate min and max of pattern segment

array min index = 1+(index-1)*maxlength;

array_max_index = index*maxlength;

%transfer the file

v_length=TSW3100writer_lvds('tsw3100 tempvector.bin',

data(array_min_index:array_max_index), twos_or_offset,complex_or_real);

transfer file(IPdigit);

TSW3100 vectorwrite end(v length, lvds or cmos, IPdigit);

end

%now we need to transfer the final pattern segment

%calculate min and max of the final pattern segment

array min index = 1+(numloads-1)*maxlength;

array max index = length(data);

%transfer the file

v length=TSW3100writer lvds('tsw3100 tempvector.bin',

data(array_min_index:array_max_index), twos_or_offset,complex_or_real);

transfer file(IPdigit);

TSW3100_vectorwrite_end(v_length,lvds_or_cmos,IPdigit);

end

```

```

else

```

```

%calculate the # of loads needed to transfer the data

numloads=ceil(length(data)/maxlength);

if numloads == 1

%Pattern is less than the maximum pattern size, so we can

%transfer all at once

v_length=TSW3100writer_cmos('tsw3100_tempvector.bin', data, twos or offset);

transfer file(IPdigit);

TSW3100 vectorwrite end(v length, lvds or cmos, IPdigit);

else

%Pattern is more than the maximum pattern size, so we must

%break the pattern into separate files and load sequentially

%sequence through the # of loads - 1 at maximum size

for index = 1:numloads-1

%calculate min and max of pattern segment

array min index = 1+(index-1)*maxlength;

array_max_index = index*maxlength;

%transfer the file

v_length=TSW3100writer_cmos('tsw3100_tempvector.bin',

data(array_min_index:array_max_index), twos_or_offset);

transfer file(IPdigit);

TSW3100 vectorwrite end(v length, lvds or cmos, IPdigit);

end

%now we need to transfer the final pattern segment

%calculate min and max of the final pattern segment

array min index = 1+(numloads-1)*maxlength;

array max index = length(data);

%transfer the file

v length=TSW3100writer cmos('tsw3100 tempvector.bin',

data(array_min_index:array_max_index), twos_or_offset);

transfer file(IPdigit);

TSW3100 vectorwrite end(v length, lvds or cmos, IPdigit);

end

end

%sub-function to transfer the data file

function transfer file(IPdigit)

% transfer file(IPdigit)

% IPdigit = x=0,1,2,3 - the last digit of IP address 192.168.1.12x

cmd str = ['tftp -I 192.168.1.12' int2str(IPdigit) ' put tsw3100 tempvector.bin

/tmp/vector']

dos(cmd str) % write the command string to matlab window

pause (0.1); % pause a short time after tftp to allow processor to catchup

%sub-function to signal the end of the data file transfer. Signals for

%the TSW3100 processor to transfer the data from the processor memory

%to pattern memory

function TSW3100 vectorwrite_end(vector_length,lvds_or_cmos,IPdigit)

% TSW3100 vectorwrite end(vector length, lvds or cmos, IPdigit)

% signal end of vector load.

% Pause (~ second/2 MB) required as TSW3100 loads from processor memory into SDRAM.

control(1)=537461024;

fp = fopen('ready rx', 'wb');

fwrite(fp,control,'ubit32');

fclose(fp);

cmd str = ['tftp -I 192.168.1.12' int2str(IPdigit) ' put ready rx /tmp/ready rx']

dos(cmd str)

%Insert pause to allow TSW3100 processor to transfer pattern

if lvds or cmos(1) == 'l'

pause(vector length/1e6);

else

```

#### 5.4 Running the TSW3100

The function **TSW3100\_vectorwrite\_load** load a pattern files and start the pattern display. The input arguments are the data pattern array **data**, **lvds\_or\_cmos** a string starting with either **I** (LVDS) or **c** (CMOS) indicating the pattern type, **twos\_or\_offset** a string starting with either **t** (twos compliment) or **o** (offset binary) indicating output pattern format, **IPdigit**, the last digit of the IP address 192.168.1.12x, and **master\_or\_slave** a string starting with either **m** (master) or **s** (slave) defines how the TSW3100 operates.

The function returns an error message if the input arguments are out of range. The main body of the function includes all the basic steps outlined in Section 2.4 Section 4.4.

```

function error msg=TSW3100 run(data, lvds or cmos, twos or offset, IPdigit, master or slave)

% error_msg = TSW3100_run(data, lvds_or_cmos, twos_or_offset, IPdigit,master_or_slave)

data = complex integer data scaled between

ŝ

ŝ

-32768 (full scale negative) and

ŝ

32767 (full scale positive)

Ŷ

lvds or cmos = a matlab string starting with 'l' for LVDS output or 'c'

ŝ

for CMOS output

÷

twos or offset = a matlab string starting 't' for twos complement or

ŝ

'o' for offset binary

2

IPdigit = IP address 192.168.1.12x where x = 0, 1, 2 or 3

% master or slave = a matlab string starting 'm' for master or 's' for slave

error_msg =[];

%round and check input data

data=round(data);

if min(min(real(data)), min(imag(data))) < -32768 | max(max(real(data)), max(imag(data))) > 32767

error msg = 'data must be between -32768 and 32767'

end

if lvds or cmos(1) ~= 'l' & lvds or cmos(1) ~= 'c'

error msg = 'lvds or cmos must be a matlab string starting with l for LVDS output or c for

CMOS output'

end

if twos or offset(1) ~= 't' & twos or offset(1) ~= 'o'

error msg = 'twos or offset must be a matlab string starting with t for twos complement or o

for offset binary'

end

if master or slave(1) ~= 'm' & master or slave(1) ~= 's'

error msg = 'master or slave must be a matlab string starting with m for master or s for

slave'

end

if IPdigit ~= 0 & IPdigit ~= 1 & IPdigit ~= 2 & IPdigit ~= 3

error msg = 'IPdigit must be an integer = 0, 1, 2 or 3'

end

if length(error msg) == 0

%stop pattern generator

TSW3100 stop(IPdigit);

%signal beginning of vector load

TSW3100 vectorwrite begin(IPdigit);

%load vector for lvds or cmos

vector length=TSW3100 vectorwrite load(data,lvds or cmos,twos or offset,IPdigit);

%write control file

TSW3100 start(vector length, lvds or cmos, IPdigit, master or slave);

error_msg = 'no error'

```

```

end

```

## 6 Generating LVDS and CMOS Test Patterns

TI provides two programs to generate test patterns for the TSW3100: **TSW3100\_MultitonePattern** (Section 6.1) and **TSW3100\_CommSignalPattern** (Section 6.3). Section 2.5 describes how to start these two TSW3100 software applications.

## 6.1 TSW3100\_MultitonePattern Software

The **TSW3100\_MultitonePattern** program can automatically generate a test pattern with single or multiple tones. The patterns can be complex or real for LVDS or CMOS outputs. The TSW3100 can be controlled directly from software interface, including loading, starting, and stopping the pattern.

Figure 21 shows the TSW3100\_MultiTonePattern Software GUI generating a pattern by using the default settings and clicking the **Create and Save/Run TSW3100** button.

| Taxas              | - Signal Char    | acteristics         |           |        |          | 2        |       |                           |           |          |          |        |        |

|--------------------|------------------|---------------------|-----------|--------|----------|----------|-------|---------------------------|-----------|----------|----------|--------|--------|

| Texas<br>struments |                  | tate (MHz) 16 Resol | ution 📘 🗖 | Random | Seed     |          |       |                           |           |          |          |        |        |

| suumenus           | 0.99 Backoff     | 215 Vect            | or size 🗖 | Invert |          |          |       | -                         | External  | Fig      |          |        |        |

|                    | -                |                     | - 20      |        |          |          |       |                           | LATEIMA   | r ig     |          |        |        |

|                    |                  | Signal Type         | 20(       | 40.    |          |          |       |                           |           |          |          |        |        |

|                    |                  | Ocomplex O Real     | 180       | ]      | -        |          |       |                           |           |          | ******   |        |        |

|                    |                  | SINC Correction     | 160       | )      | +        |          |       | +                         | <u>  </u> |          |          |        |        |

|                    |                  | Data Band Enable    | 140       |        | 4        |          |       | <b>.</b>                  | <b>  </b> |          | -        | j.     | CALLER |

|                    |                  | 0 DAC IF Min (MHz   | ) 😨 120   |        |          |          |       | ļ                         |           |          |          |        |        |

|                    |                  | 1000 DAC IF Max (MH |           | ÷      | 1        |          |       |                           |           |          |          |        |        |

|                    |                  | 1 DAC Interp        | plitu     |        |          |          |       |                           |           |          |          |        |        |

|                    |                  |                     | _ ¥ 8     | ]      |          |          |       |                           |           |          |          |        |        |

| one Groups         |                  |                     | 60        | )      |          |          |       |                           |           |          |          |        |        |

| Enable Tor         | ne BW # Tone     | Center Gain (dB)    | 40        |        |          | <b>N</b> | and a | h dia a                   |           |          | Baine.   |        | -      |

| Group 1            | 1 1 10           | 00.1 0              | 20        | )<br>[ |          |          | 33415 | Contraction of the second |           |          |          |        |        |

|                    | III IS MILL MALE |                     |           |        |          |          |       | - "N                      |           | 1        | Ť.       |        |        |

| Group 2            | 1 1 10           | 0.1 0               | 3         | -5     | -4 -     | 3 -2     |       |                           | 0 1       | N        | 2 3      | 3 4    |        |

|                    |                  |                     |           | T      | SW3100   | Cont     | rol   | Freque                    | ncy (Hz)  | _        |          |        | x 10   |

| Group 3            | 1 1 10           | 10.1 0              |           | 1      | 💿 master | OLV      | 1     | ⊙ Tw                      | o's Comp  |          | AD and I | Run Sh | art    |

|                    |                  |                     |           |        | 🔿 slave  | 00       | MOS   | Oott                      | set Bin   | [♥] Inte | erleaved | Sto    | ip.    |

|                    | 1 10             | 0.1                 |           |        | ennweil  |          |       | -                         |           | 192.1    | 68.1.12  | 3      | -      |

| Group 4            |                  |                     |           | -      |          |          |       |                           |           |          |          |        |        |

| Group 4            |                  |                     |           |        |          |          |       |                           |           |          |          |        |        |

| Group 4            |                  |                     |           |        |          |          |       |                           |           |          |          |        |        |

|                    | nd Save/Rup T    | \$\\\/3100          |           |        |          |          |       |                           |           |          |          |        |        |

|                    | nd Save/Run T    | SW3100              |           |        |          |          |       |                           |           |          |          |        |        |

Figure 21. TSW3100\_MultiTonePattern Graphical User Interface